# DEFENCE AND SPACE

Spacecraft Equipment

# High Performance Data Processor (HPDP)

а

000

## KEY FEATURES OF THE HPDP BOARD

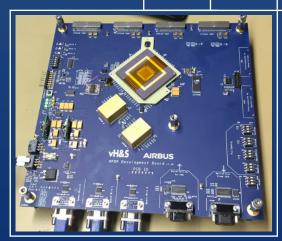

- Based on XPP III Array Processor from PactXPP Technologies providing 40 Giga operations per second (End-of-Life)

- 4 Mbyte on-chip SRAM

- 5Gbit of on-board SDRAM

- Streak observations algorithms to detect space debris:

- - HPDP outperforms Desktop PC by factor 12

- Moon Asteroid Strike + Vessel Detection

- Performance of the implementation exceeds the required 1kfps

- Autonomous Navigation for Lander Units and Rovers

- RGB to Greyscale, Filtering and Corner detection within 4 ms

- 4 x 1.1 Gbit/s Streaming Ports compatible with HSSL

The High Performance Data Processor is a building block for very high reliability, radiation hard data processing. It is characterized by the ability to sustain a high data throughput combined with a high performance level and the flexibility to adapt target applications to emerging standards and improvements. The potential of the HPDP lies in the processing capability of

()

а

high data volumes in the signal-processing domain, especially where flexibility and in-orbit re-programmability or reconfiguration is required.

• Fully reprogrammable platform

• 3 SpaceWire interfaces for monitor and control operating at 100 Mbps on each channel with routing capability

# MAIN APPLICATION FIELDS

- High Performance Processing (e.g. Image Processing)

- Low power Data Processing Unit

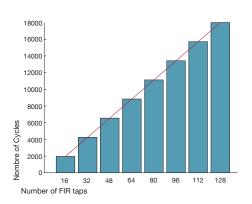

- Application Implementations (exemplary@250 MHz)

# **CHARACTERISTICS OF HPDP-40 CHIP**

40 ALU Processing Array (PAEs), arranged in a rectangular array, featuring:

- 40 ALU Processing Array Elements (PAEs 16-bit) running with 250MHz each

- 2 Harvard type VLIW 16-bit processor cores (FNCs) running at 125MHz

- 256 Kbit high speed on-chip RAM

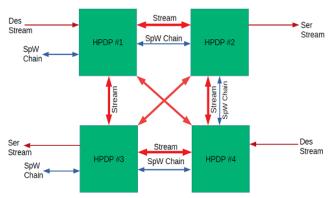

# **CASCADING OF HPDP BOARDS**

#### Hidden: JTAG / ID / Spw Control

# SOFTWARE SUPPORT

- Software Debug Interfaces:

- Run-time JTAG Debug Support Interface for register access and array debugging

- Software upload and software monitoring via SpaceWire

- Multi-chip simulation environment available

- Example algorithm implementations available

- GNU C-compiler and assembler tool targeted for the HPDP processor cores and array elements (FNC-PAEs).

- Stand-alone simulator for the FNC-PAEs

- Editor and NML code compiler for the HPDP Array.

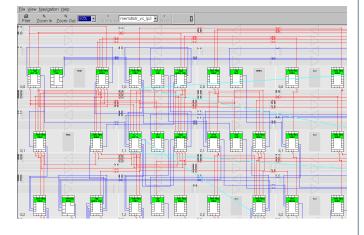

- HPDP Array visualizing tool for the HPDP application developer (see snapshot).

- Multi-chip simulator

#### **CHARACTERISTICS OF HPDP-40 CHIP** With 2 097 152 or 524 288 131 072 Without 32 768 External 8192 RAM 2048 512 Nombre of Cycles 128 32 2 512 1024 2048 4096 32 64 128 256 Size of FFT A 512FFT on a LEON processor takes ~40K cycles HDPD is a factor ~10 more efficient

### Fully radiation hardenend processor platform:

Based on STM Rad hard 65nm CMOS technology platform for space applications (ITAR free)

## **Environmental Operation conditions:**

| Temperature                    | -55 °C to +125 °C  |

|--------------------------------|--------------------|

| TID Tolerance                  | >100 kRad          |

| Single Event Latch-up Immunity | up to 60Mev/mg/cm2 |

|                                | at 125°C           |

| Life Time in-orbit:            | 20 years           |

HPDP / Non-contractual document, subject to changes. This document shall not be reproduced, in whole or in part, without prior consent. © 2020 Airbus Defence and Space SAS

# Airbus Defence and Space

spacecraft.equipment@airbus.com